Disclaimer: Dieser Thread wurde aus dem alten Forum importiert. Daher werden eventuell nicht alle Formatierungen richtig angezeigt. Der ursprüngliche Thread beginnt im zweiten Post dieses Threads.

CPU-Entwurf mit VHDL (Erfahrungsberichte)

Moin moin,

hat hier jemand zufällig schonmal “CPU-Entwurf mit VHDL” belegt und kann mal berichten, wie das Modul so war. Wie war das Modul an sich, wie war die Klausur, gab es Übungen und wenn ja, wie waren diese dann? Mich interessiert das einfach aus dem Grund, da ich momentan mit dem Gedanken spiele das Modul nächstes Semester zu belegen und dann auch noch eine Bachelor-Arbeit in dem Themengebiet zu verfassen. Hab mich bei der Website vom Lehrstuhl 3 schon mal umgeschaut und mir die Themen von Bachelor-Arbeiten angeschaut und bin dann oft auf den Begriff CPU-Entwurf gestoßen, da wärs ja nicht dumm wenn man sich mal anschaut, wie sowas überhaupt geht, denn soooo leicht klingt das nicht.

Edit: Es geht mir um das Moudl (CPU-Entwurf mit VHDL mit 7,5 ECTS!!)

Habe das Modul im Sommersemester 2019 bei Marc Reichenbach belegt.

Ich fand die Vorlesung sehr cool, Marc ist ein toller Dozent. Man lernt einiges ueber VHDL und allgemein Hardware, und dann spaeter ueber CPUs, wo sich afaik auch einiges mit Rechnerarchitektur ueberschneidet: es geht hier viel ueber Pipelining/Hazards, aber dann auch ueber ein paar “Higher-Level”-Themen, wie Parallelitaet.

In der Uebung baut man dann schrittweise eine MIPS-CPU: Register, ALU, Speicher, und letztendlich auch Pipelining. Vor allem das Pipelining ist da nicht gerade trivial; trotzdem ist es mega interessant, weil man dann wirklich eine funktionierende Minimal-CPU (inklusive Pipelining) hat, die auf einem FPGA laeuft. Es gibt dann auch noch eine Wahlaufgabe, wo man aus verschiedenen Themen waehlen kann: z.B. eine FPU bauen, oder die CPU Multicore macht.

Die Pruefung ist dann ein gewoehnliches 30 minuetiges Gespraech, das eigentlich sehr entspannt ablaeuft, wenn man die Aufgaben alle gemacht hat und die Folien nochmal durchgeht. Bzgl. Hardware wurde oft gar nicht so sehr auf die komplizierten Details eingegangen, was damals meine Befuerchtung war, weil ich das etwas schwieriger fand. (Ich habe auch ein Pruefungsprotokoll geschrieben.)

Insgesamt kann ich das Modul also sehr empfehlen, v.a. wenn dir so was wie GRa gefallen hat.

Das klingt schon mal nach dem was ich mir gewünscht hatte. Also Gra fand ich ziemlich geil und wenn da wieder Sachen aufgegriffen werden von Gra und auch erweiterte Themen dran kommen, dann klingt das für mich ziemlich vielversprechend!! Danke dir für den Bericht!

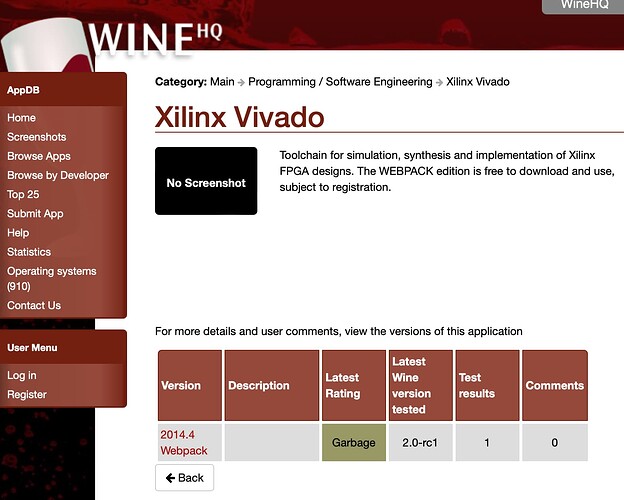

Gibt es eine unixoidere IDE/Toolchain für FPGAs als Vivado die ihr für macos empfehlen könnt?

EDIT: Ich probiere eine VSC Extension aus und schaue wie viel sich damit machen lässt: TerosHDL | TerosHDL